Multisim |

您所在的位置:网站首页 › 74ls138功能测试实验报告 › Multisim |

Multisim

|

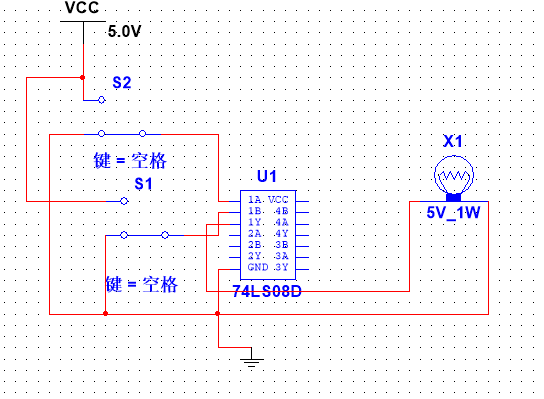

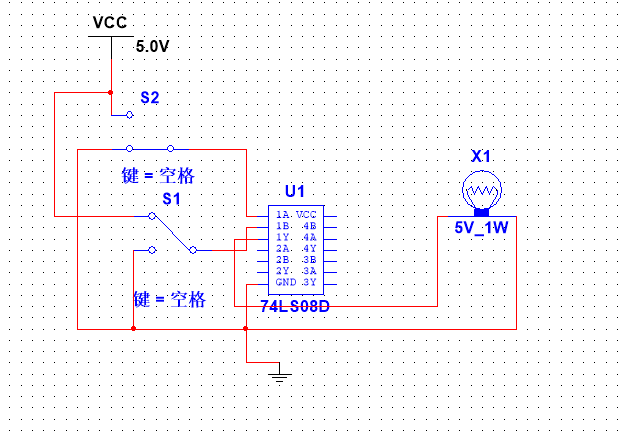

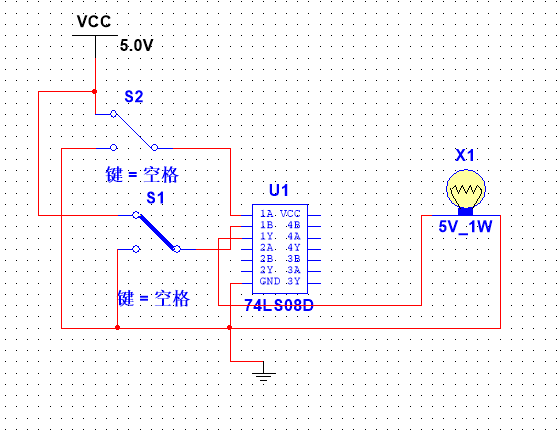

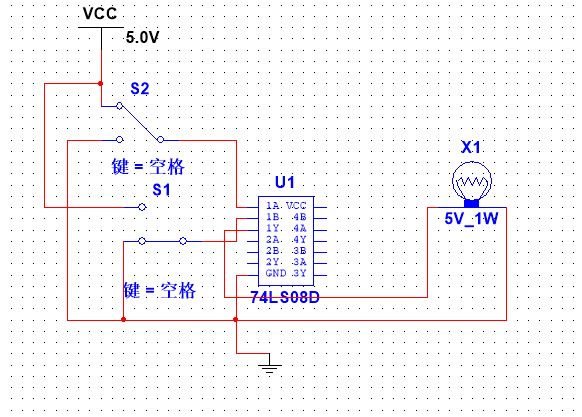

一. 实验目的 了解TTL门电路的外观封装、引脚分布和使用方法。 掌握数字电路试验台、万用表和示波器的使用方法。 掌握TTL与门、或非门和异或门的逻辑功能。 认识门电路对信号的控制作用。二.实验内容 1.原始数据 表1 74LS08的测试表格 输入端 输出端 K1 K2 L1 0 0 0 0 1 0 1 0 0 1 1 1

表2 74LS02的测试表格 输入端 输出端 K1 K2 L1 0 0 1 0 1 0 1 0 0 1 1 0

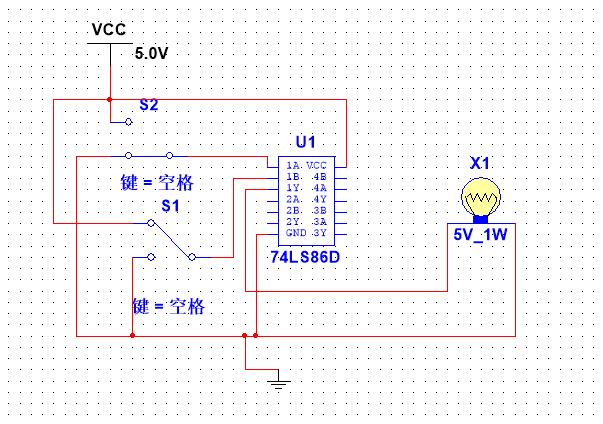

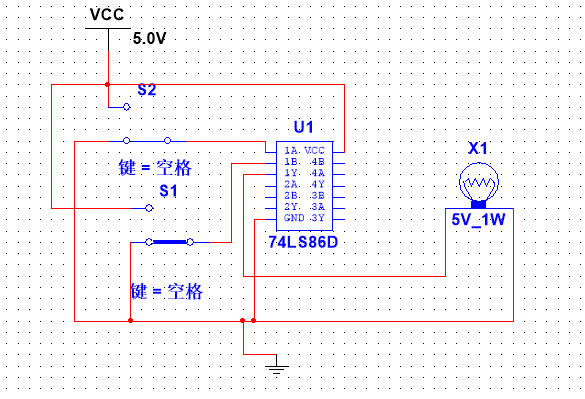

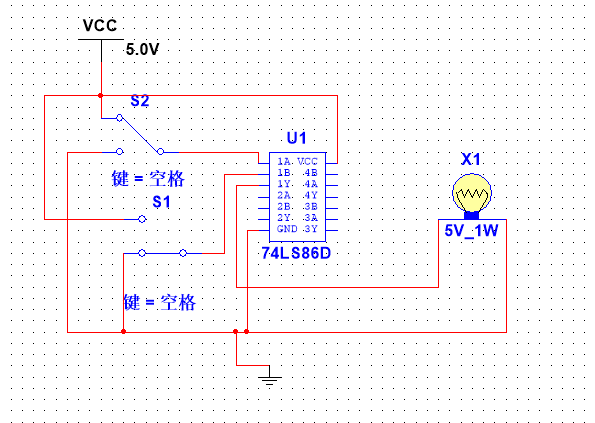

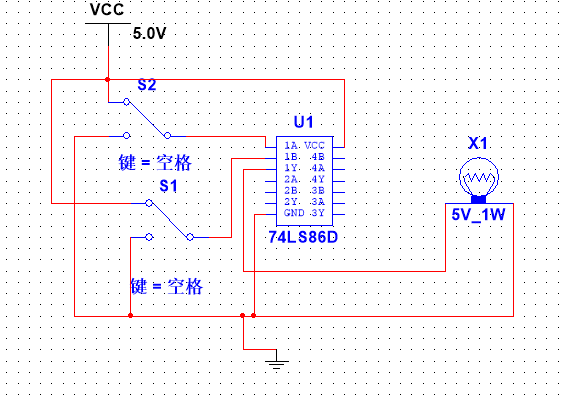

表3 74LS86的测试表格 输入端 输出端 K1 K2 L1 0 0 0 0 1 1 1 0 1 1 1 0

2.整理分析实验数据,总结各基本门的逻辑功能 1)74LS08的逻辑功能:当A、B均为高电平时,Y为高电平“1”;A、B中有一个为低电平或二者均为低电平时,Y为低电平“0” 2)74LS02的逻辑功能:当A、B均为低电平时,Y为高电平“1”;A、B中有一个为高电平或二者均为高电平时,Y为低电平“0” 3)74LS86的逻辑功能:当A、B电平状态不同时,Y为高电平“1”;当A、B电平状态相同时,Y为低电平“0” 3.思考题 (1)与门什么情况下输出高电平?什么情况下输出低电平?与门不用的输入端应如何处理? 答:输入全为1的时候,输出才为1;输入有0时,输出则为0。 与非门中不用的输入端最好是接高电平。

(2)或非门在什么情况下输出高电平?什么情况下输出低电平?或非门不用的输入端应如何处理? 答:只要有一个输入是 1 ,输出就为 0 ;输入全为 0 ,输出才为 1 接地.或非门输出端常态为高电平1.只要有一个高电平1,则输出为低电平0.所以多余的输入端接地置为0.不会影响其逻辑功能.

(3)如果与非门的一个输入端接连续时钟脉冲,那么:1其余输入端是什么状态时,允许脉冲通过?脉冲通过时,输出端波形与输入端波形有何差别?2其余输入端是什么状态时,不允许脉冲通过?这种情况下与非门输出是什么状态? 答:其余输入端为高电平,允许脉冲通过。输出端波形。与输入端波形相位相反。 其余输出端为低电平。不允许脉冲通过。这种情况下,与非门输出为高电平。输出波形为一条直线。与非门为关闭状态。 4、仿真效果 1)74LS08

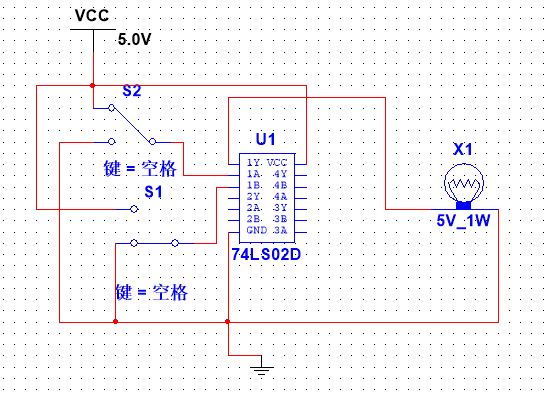

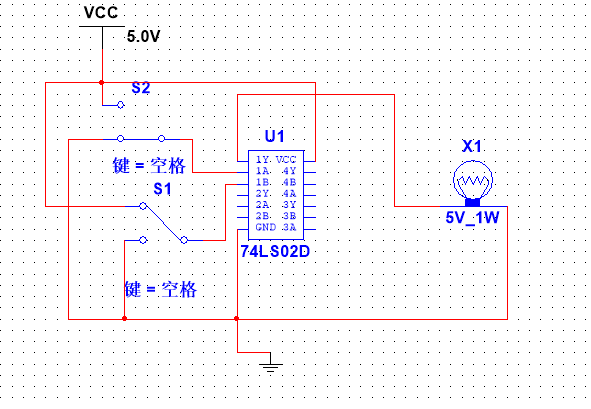

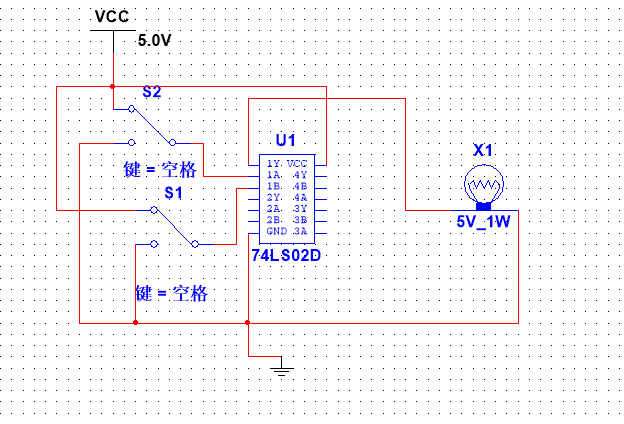

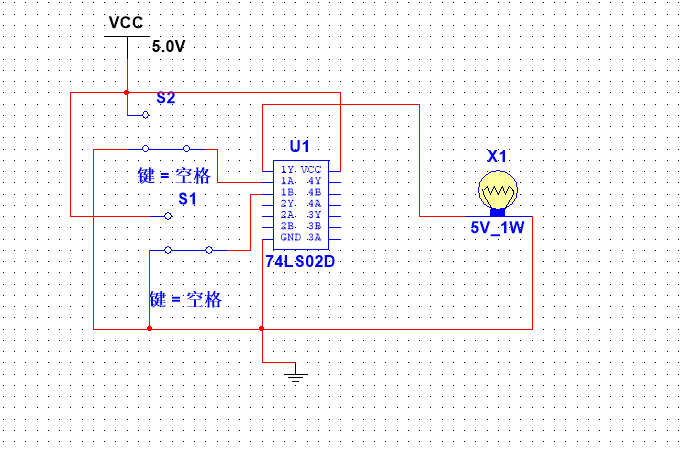

2)74LS02

3)74LS86

|

【本文地址】

今日新闻 |

推荐新闻 |