74ls109引脚图及功能详解 |

您所在的位置:网站首页 › 74ls107功能 › 74ls109引脚图及功能详解 |

74ls109引脚图及功能详解

|

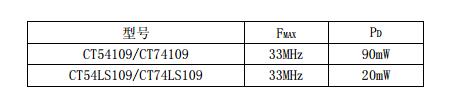

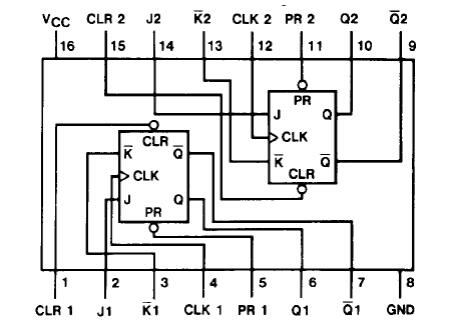

本文首先介绍了74ls109引脚图及功能,其次阐述了74ls109功能表、极限值,最后介绍了74ls109推荐工作条件以及静态特性和动态特性,具体的跟随小编一起来了解一下。 74ls109为带预置和清除端的两组 J-K 触发器,共有 54/74109 和 54/74LS109 两种线路结构型式,其主要电特性的典型值如下:

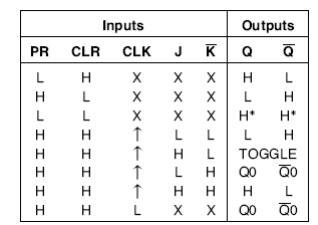

引脚功能: CLK1、CLK2———— 时钟输入端 J1、J2、K1、K2——— 数据输入端 Q1、Q2、/Q1、/Q2—— 输出端 CLR1、CLR2————直接复位端(低电平有效) PR1、PR2——————直接置位端(低电平有效) 74ls109功能表

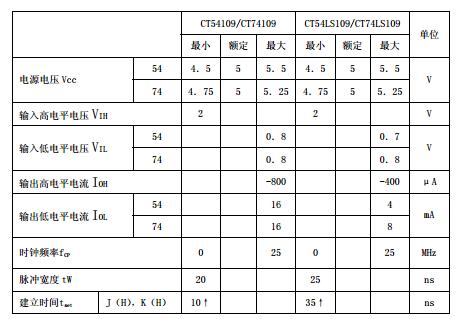

说明:H-高电平 L-低电平 X-任意 ↑-低到高电平跳变 Q0-稳态输入建立前Q 的电平 /Q0-稳态输入建立前/Q 的电平 H*-不定 74ls109极限值极限值电源电压------------------------------------------------7V 输入电压 54/74109-----------------------------------------5.5V 54/ 74LS109---------------------------------------7V 工作环境温度 54×××------------------------------ -55~125℃ 74×××------------------------------------0~70℃ 贮存温度-------------------------------------- -65~150℃ 74ls109推荐工作条件

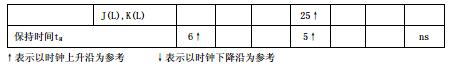

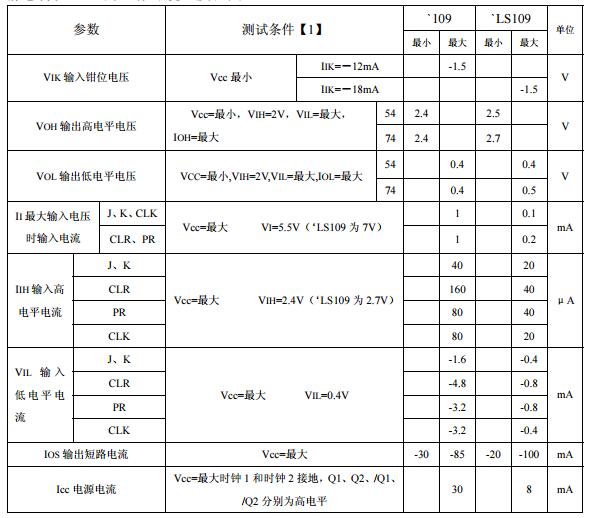

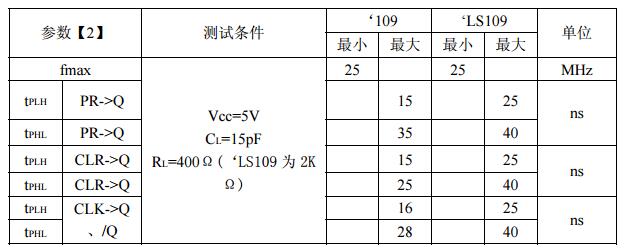

测试条件中的“最大”和“最小”用推荐工作条件中的相应值 74ls109动态特性(TA=25℃)

fmax-最大时钟频率 tPLH-输出由低到高电平传输延迟时间 tPHL-输出由高到低电平传输延迟时间 推荐下载:《74ls109中文资料》 |

【本文地址】

今日新闻 |

推荐新闻 |