组合逻辑电路一 |

您所在的位置:网站首页 › 74ls04逻辑功能 › 组合逻辑电路一 |

组合逻辑电路一

0 📂实验目的

0 📂实验目的

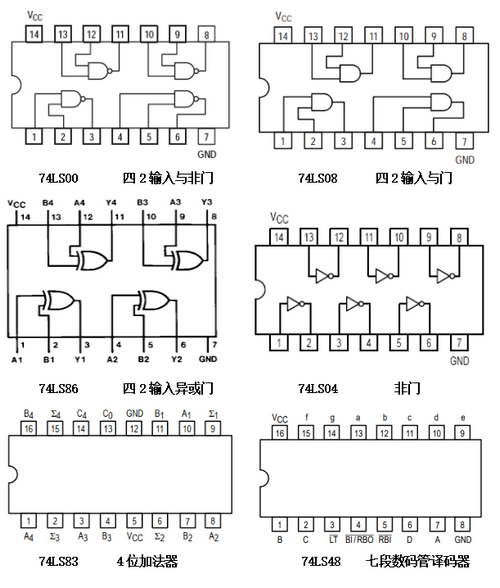

(1)掌握组合逻辑电路的功能测试。 (2)掌握半加器和全加器的逻辑功能。 (3)熟悉加法器、数码管、译码器的使用。 1 📂实验仪器及材料 2 📂实验内容及步骤

2 📂实验内容及步骤

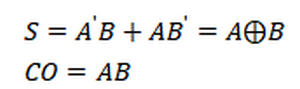

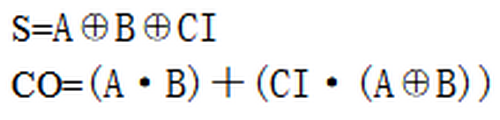

测试半加器的逻辑功能 如果不考虑有来自低位的进位将两个1位二进制数相加,称为半加。实现半加器运算的电路叫做半加器。如果A、B是两个加数,S是相加的和,CO是向高位的进位,则半加器的逻辑表达式为:

根据表达式由一个异或门和一个与门画出电路图如下,按照表格测试数据。

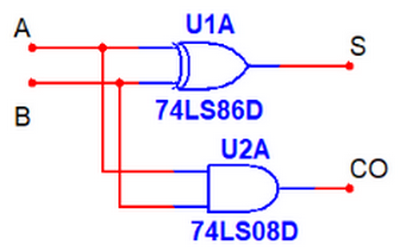

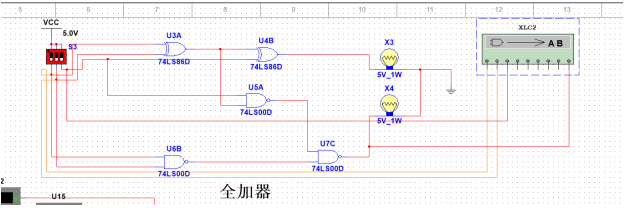

A B S CO 0 0 0 0 0 1 1 0 1 0 1 0 1 1 0 1 设计全加器 在将两个多位二进制数相加时,除了最低位以外,每一位都考虑来自低位的进位,即将两个对应位的加数和来自低位的进位3个数相加。这种运算称为全加,所用的电路称为全加器。 要求:用异或门(74LS86)和与非门(74LS00)组成全加器,并测试全加器的逻辑功能 设计方法: (1)定义输出输出,CI来自低位的进位,A、B加数,S相加的和,CO向高位的进位。 (2)根据二进制加法运算规则列出1位全加器的真值表。

(3)由真值表得到S和CO的逻辑表达式(可以用卡诺图或者合并1的方法化简)。

(4)再次化简S和CO表达式,使表达式能用所给逻辑门(异或门和与非门)组成电路。

(5)画电路图。

(6)按照表格数据输入,测量输出,验证电路是否符合全加器的逻辑功能。

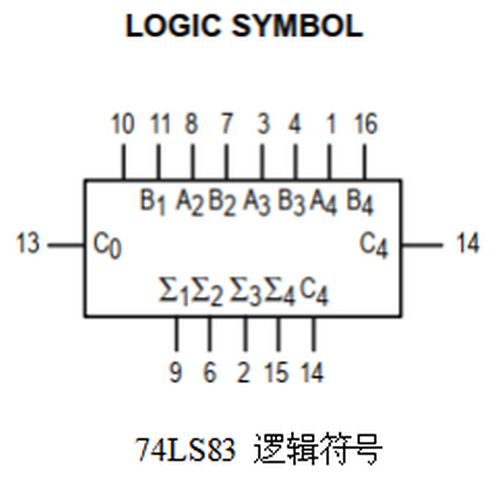

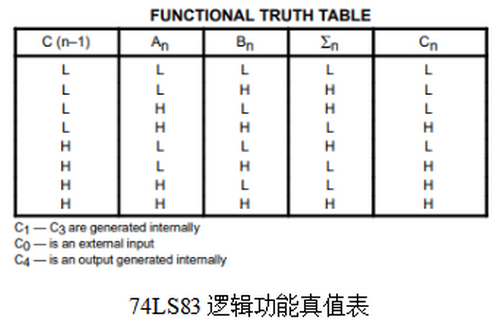

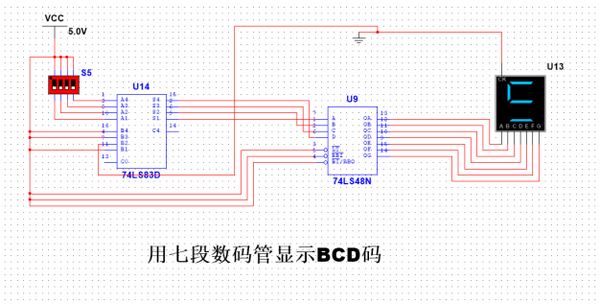

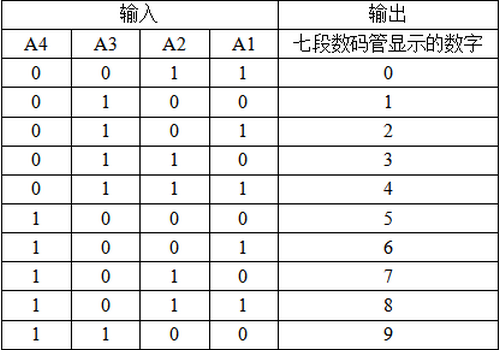

用加法器(74LS83)设计一个代码转换电路,将余三码转换成BCD码 74LS83是4位超前进位加法器,可以实现四位二进制数的加法运算,其中A为加数,B为被加数,Z为相加的和,C0为低位向高位的进位,C4为输出的进位。

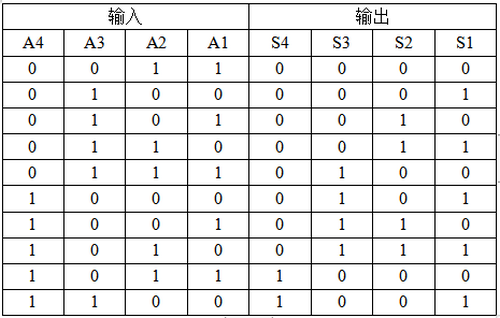

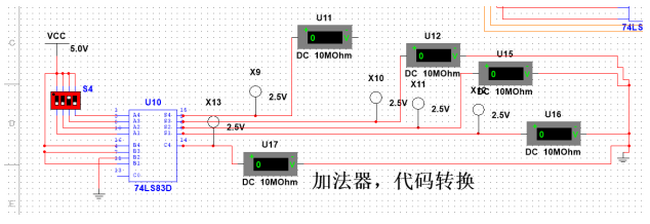

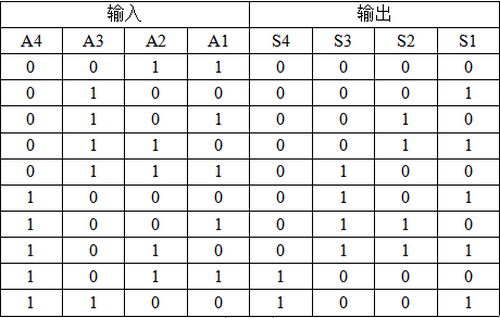

设计方法: (1)以余三码为输入,8421码为输出,列出代码转换电路的真值表

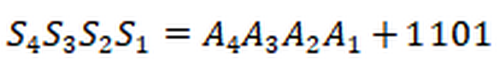

(2)观察真值表,与所代表的二进制数始终相差1101,所以得到:

(3)根据表达式画电路图

(4)按照表格数据输入,测量输出,验证电路。

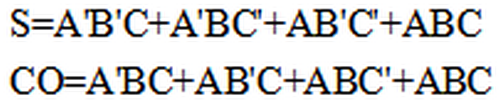

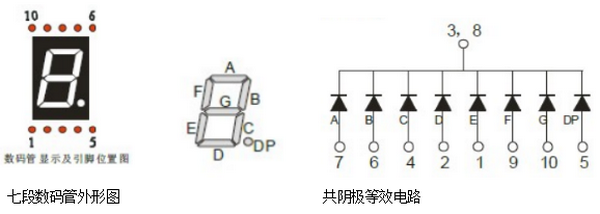

用七段数码管显示内容3中的BCD码 七段数码管由七段发光二极管构成,分为共阳极、共阴极两种形式。共阴极数码管将发光二极管的阴极接在一起作为公共极,公共极接低电平,当驱动信号为高电平时,阴极二极管发光。

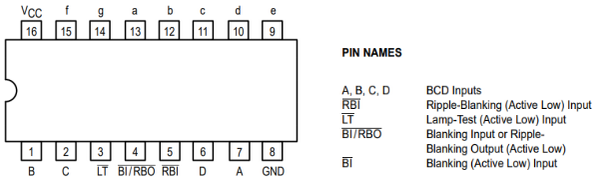

显示译码器将BCD码译成数码管所需要的驱动信号,使数码管显示出相应的十进制数字。共阴极数码管的译码器74LS48管脚图如下:

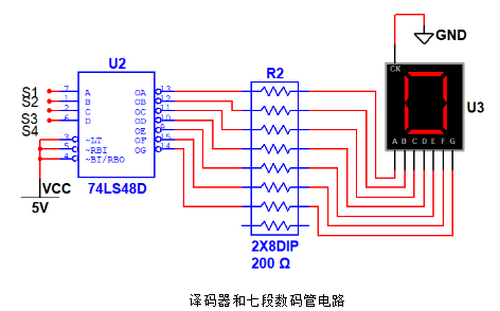

当LT'(灯测试输入)、RBI'(灭零输入)、BI/RBO'(灭灯输入/灭灯输出)都为高电平时,输入端DCBA输入的BCD码被译码成数码管所需要的驱动信号。 在译码器和数码管之间需要加限流电阻。

设计方法: (1)连接译码器和七段数码管,组成七段数码管显示电路,如上图所示。 (2)将内容3中“余三码转换成BCD码电路”的输出信号S4S3S2S1与“七段数码管显示电路”的输入信号S4S3S2S1连接在一起(替换成自己的电路图),注意四位数据的高低顺序。

(3)输入余三码,观察并记录七段数码管的显示。  3 📂实验报告以及实验电路图等下载链接

数字逻辑实验:内含实验报告,和所用实验软件,还有实验电路图,其中包括七个实验实验报告中的各个实验的答案都已填好!!!-C++文档类资源-CSDN文库

3 📂实验报告以及实验电路图等下载链接

数字逻辑实验:内含实验报告,和所用实验软件,还有实验电路图,其中包括七个实验实验报告中的各个实验的答案都已填好!!!-C++文档类资源-CSDN文库

|

【本文地址】

今日新闻 |

推荐新闻 |