深入浅出逻辑组合电路(2) |

您所在的位置:网站首页 › 7485n引脚图 › 深入浅出逻辑组合电路(2) |

深入浅出逻辑组合电路(2)

|

深入浅出逻辑组合电路(2)

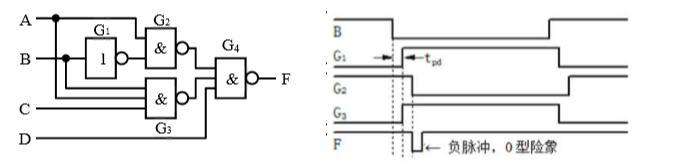

门电路中的冒险现象

通常讨论逻辑电路时,只从抽象的逻辑角度进行描述,不考虑实际电路中必然存在的信 号传输时延和信号电平变化时刻对逻辑功能的影响。逻辑门的传输时延以及多个输入信号变 化时刻不同步,可能会引起短暂的输出差错(俗称毛刺),这种现象称为逻辑电路的冒险现 象(简称险象)。险象的持续时间虽然短暂,危害却不可忽视,尤其在驱动时序电路时,险象可能造成严重后果。 1.冒险现象的来源 信号传输时延引起的冒险现象称为逻辑险象输入信号的变化只引起一个毛刺,称为静态险象多个输入信号的变化时刻不同步引起的现象称为功能险象可以把险象分为 0 型险象和 1 型险象:输出信号中的毛刺为负向脉冲的险象称为 0 型险象,为正向脉冲时称为 1 型险象。这里只对逻辑门时延引起的静态险象做初步讨论 举个例子写出图所示电路的输出信号表达式,求出 ACD=111 时的函数值。 设逻辑门的传输时延为 Tpd,画出波形图,并判断电路是否存在险象。  接着分析,如果ACD=111,F始终为1,可以发现,不管B怎么变化,F的值始终为1 接着分析,如果ACD=111,F始终为1,可以发现,不管B怎么变化,F的值始终为1

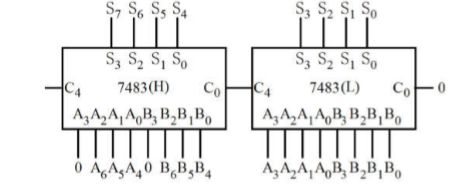

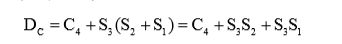

如图所示: 采用级联扩展7483级联实现两个 7 位二进制数相加的电路图,注意高位芯片 7483(H)A3、B3置 0,两 个 7 位二进制数之和不超过 8 位,因此,结果由图中 S7~S0输出。注意,该电路两个模块内部的进位是先行进位,而级联模块之间的进位则是串行进位。 7483应用 4位全加器7483实现1位8421码加法器解题思路: 7483是4位二进制加法器,其进位规则是逢16进1。而8421码表示的是十进制数, 进位规则是逢10进 1。用 7483 将两个 1 位 8421 码相加时,当和≤9 时,结果正确当和≥10 时,由于 7483 将输入的 BCD 码当作二进制数相加,将出现差错。例如,当和为(10)10 时,按 BCD 码运算,应该进位。用 7483 实现 BCD 码相加, 关键在于确定何时应该对结果进行修正,以及如何修正。 两个 1 位十进制数相加,和的取值范围是 0~ 18,将该范围内数值的二进制数和 8421 码列于表 4-21,以便寻找将二进制结果转换为 8421 码的规律。 当数值在 10 以上时,应该用 2 位 8421 码,个位用 D8D4D2D1表示,考虑到十位数仅为 0 或 1,8421 码 为前3位为0,只有最低位是变量,表中用DC表示。 比较表中的二进制数和 BCD 码可以发现,当 N10≤9时,二进制数与8421码相同;当N10≥10时, 8421 码比相应的二进制数大 6。 判断 N10≥10 的电路就用表中的 DC,当 C4=1、 或者 S3=1 且 S2和 S1中至少有一个为 1 时,DC=1。 据此写出表达式

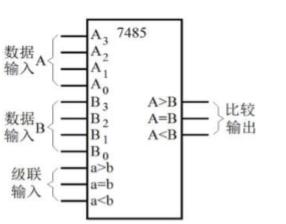

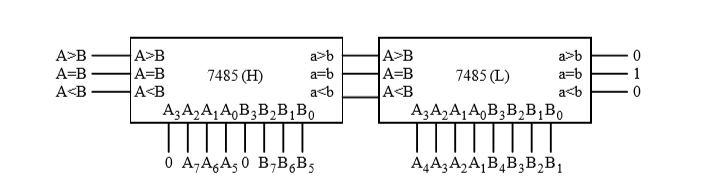

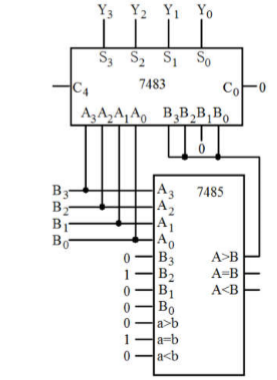

7485 的三个级联输入端用于连接低位芯片的三个比较输出端,实现比较位数的扩展。 图 4-46 是用两片 7485 级联实现的两个 7 位二进制数比较器,参与比较的两个 7 位二进制数 是 A7~A1和 B7~B1,比较结果由***高位芯片输出***。两片 7485 中,高位芯片 7485(H)的两 个最高位 A3和 B3置为相等(都置为 0,也可以都置为 1),低位芯片 7485(L)的级联输入 端“a=b”置 1,其余两个端子置 0,以确保当两个 7 位二进制数相等时,比较结果由***低位芯片的级联输入信号决定***,输出 A=B 的结果。

|

【本文地址】

今日新闻 |

推荐新闻 |

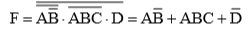

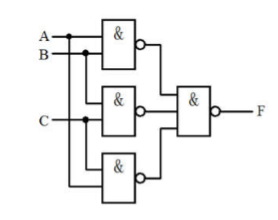

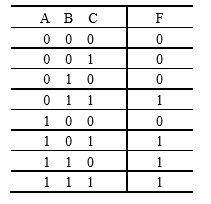

分析图所示电路 按照先写逻辑函数表达式-列出真值表的步骤一步一步来

分析图所示电路 按照先写逻辑函数表达式-列出真值表的步骤一步一步来

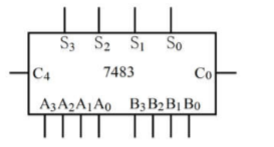

7483 是具有先行进位功能的 4 位二进制全加器, 先行进位设计改变了加法器的进位产生方式,使电路的 工作速度大幅提高,输入/输出端之间的最大时延仅为 4级门时延,7483的惯用逻辑符号如图4-41所示。74283 与 7483 的逻辑功能完全相同,只是芯片管脚排列不同

7483 是具有先行进位功能的 4 位二进制全加器, 先行进位设计改变了加法器的进位产生方式,使电路的 工作速度大幅提高,输入/输出端之间的最大时延仅为 4级门时延,7483的惯用逻辑符号如图4-41所示。74283 与 7483 的逻辑功能完全相同,只是芯片管脚排列不同