FPGA学习笔记(一):计数器 |

您所在的位置:网站首页 › 60进制计数器仿真需要程序吗 › FPGA学习笔记(一):计数器 |

FPGA学习笔记(一):计数器

|

目录 一、逻辑设计 1.端口设计 2.波形图绘制 二、程序设计 1.计数器代码 2.仿真代码 3.仿真结果 总结 使用Verilog语言设计一个3bit的计数器电路 一、逻辑设计 1.端口设计

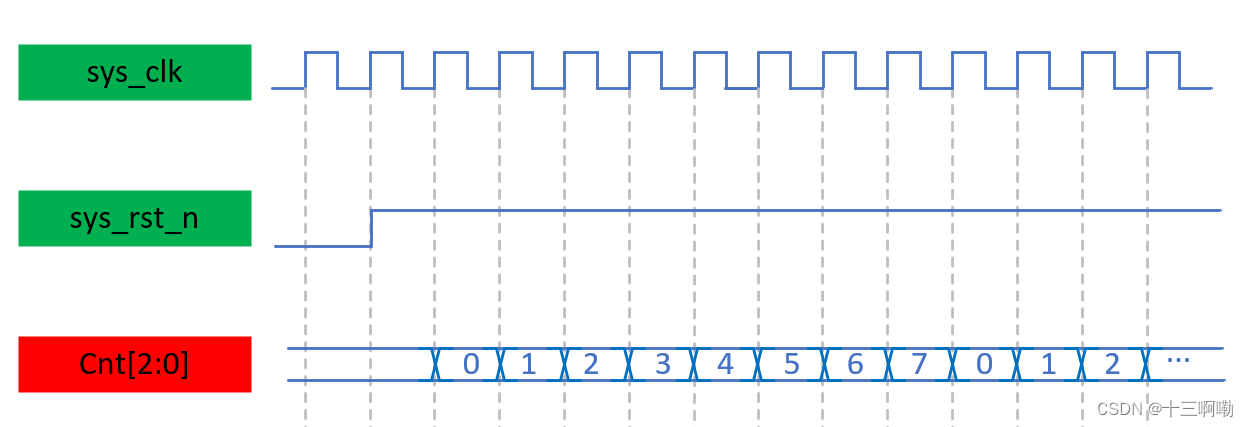

模块的输入端口包含系统时钟sys_clk、复位信号sys_rst_n;输出端口包含3bit的计数器信号cnt[2:0]。 2.波形图绘制

每个时钟上升沿之后,计数器的值就加1,cnt循环从0计数到7,每当计数器计数到最大值时,就会从零开始重新累加。 二、程序设计根据波形图使用Verilog编写计数器(counter.v)代码 1.计数器代码代码如下: module counter( input sys_clk, // 系统时钟信号 input sys_rst_n, // 系统复位信号(低电平有效) output reg [2:0] cnt // 输出计数器值,3位宽度 ); always @(posedge sys_clk or negedge sys_rst_n) begin if (!sys_rst_n) // 如果复位信号为低电平 cnt |

【本文地址】

今日新闻 |

推荐新闻 |