CD4518简易数字计时电路 含Proteus仿真原理图 |

您所在的位置:网站首页 › 60进制计数器仿真实验视频 › CD4518简易数字计时电路 含Proteus仿真原理图 |

CD4518简易数字计时电路 含Proteus仿真原理图

|

设计总体思路、基本原理和框图

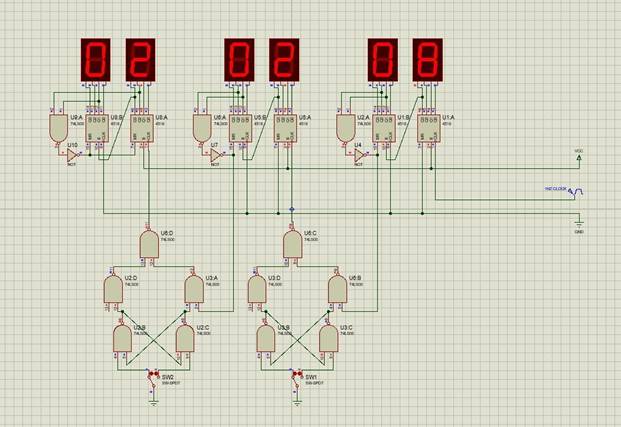

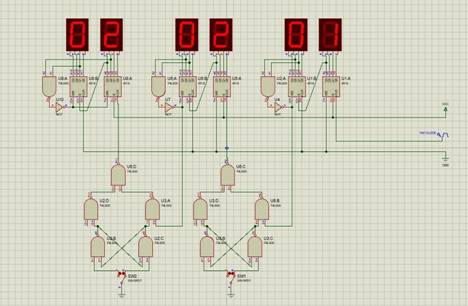

1.1 项目及要求项目:简易数字计时电路 要求:设计一简易的计时装置。能显示“小时”(0~23 时)、分(0~59 分)和秒(0~59 秒)。小时、分、 秒的十位的零均不予以现实。 仿真原理图如下(proteus仿真工程文件可到本帖附件中下载)

51hei.gif (55.7 KB, 下载次数: 173) 下载附件 2023-5-21 17:53 上传 1.2 设计思路“时、分、秒”计时器采用 CD4518 分别构成二十四进制(”时”计时器)和六十进制(“分、秒” 计时器)计数器,一个 4518 芯片里有 2 个十进制计数器,采用异步计数,反馈置零的方法即可达到 60 进 制的计数器。 在刚接通电源或者时钟走时出现误差时,则需要进行时间的校准。置开关在手动位置,分别对“时、 分”单独计数,计数脉冲由单次脉冲或连续脉冲输入。校时电路由与非门和两个开关组成,实现“时、分” 的校准。 1.3 基本原理 脉冲产生原理:NE555 采用的是多谐振荡器电路,其 R1=R2=2.4K,C1=0.1uF,C2=0.01uF,用其产生2KHz 的脉冲,然后用 CD4518 进行分频,在分频电路中先进行三次 10 分频,CD4518 使用 EN 使能端进行分 频,然后进行 2 分频,用 CP 脉冲端,使频率分到1Hz。 计数原理:时间计数电路由秒个位和秒十位计数器,分个位和分十位计数器及时个位和时十位计数器 电路构成,其中秒个位和秒十位计数器,分个位和分十位计数器为 60 进制计数器,而根据设计要求,时个位和时十位计数器为 24 进制计数器。

51hei.png (19.82 KB, 下载次数: 170) 下载附件 2023-5-21 17:48 上传 2.单元电路设计 2.1 电子元件介绍 2.1.1 CD4158 芯片CD4518 是二、十进制(8421 编码)同步加计数器,内含两个单元的加计数器。每单个单元有两个时 钟输入端 CLK 和 EN,可用时钟脉冲的上升沿或下降沿触发。可知,若用 ENABLE 信号下降沿触发,触发信 号由 EN 端输入,CLK 端置“0”;若用 CL℃K 信号上升沿触发,触发信号由 CL℃K 端输入,ENABLE 端置“1”。 RESET 端是清零端,RESET 端置“1”时,计数器各端输出端 Q1~Q4 均为“0”,只有 RESET 端置“0”时, CD4518 才开始计数。CD4518 是一个同步加计数器,在一个封装中含有两个可互换二/十进制计数器,其功 能引脚分别为 1~7 和 9~{15}。该 CD4518 计数器是单路系列脉冲输入(1 脚或 2 脚;9 脚或10 脚),4  路 BCD 码信号输出(3 脚~6 脚;{11}脚~{14}脚)。 路 BCD 码信号输出(3 脚~6 脚;{11}脚~{14}脚)。

图 2.1.1-1 CD4518 引脚排列及逻辑符号

工作原理:

图 2.1.1-1 CD4518 引脚排列及逻辑符号

工作原理:CD4518 采用并行进位方式,只要输入一个时钟脉冲,计数单元 Q1 翻转一次;当 Q1 为 1,Q4 为 0 时, 每输入一个时钟脉冲,计数单元 Q2 翻转一次;当Q1=Q2=1 时,每输入一个时钟脉冲 Q3 翻转一次;当 Q1=Q2=Q3=1 或 Q1=Q4=1 时,每输入一个时钟脉冲 Q4 翻转一次。这样从初始状态(“0”态)开始计数,每 输入 10 个时钟脉冲,计数单元便自动恢复到“0”态。若将第一个加计数器的输出端 Q4A 作为第二个加计 数器的输入端 ENB 的时钟脉冲信号,便可组成两位8421 编码计数器,依次下去可以进行多位串行计数。 图 2.1.1-2 CD4518 工作原理 CD4518 有两个时钟输入端 CP 和 EN,若用时钟上升沿触发,信号由 CP 输入,此时 EN 端为高电平(1), CD4518 有两个时钟输入端 CP 和 EN,若用时钟上升沿触发,信号由 CP 输入,此时 EN 端为高电平(1),

图 2.1.2-1 74LS00 引脚图 图 2.1.2-2 74LS00 符号

与非门的逻辑功能是:当输入端中有一个或一个以上是低电平时,输出端为高电平;只有当输入端全 图 2.1.2-1 74LS00 引脚图 图 2.1.2-2 74LS00 符号

与非门的逻辑功能是:当输入端中有一个或一个以上是低电平时,输出端为高电平;只有当输入端全

部为高电平时,输出端才是低电平(即有“0”得“1”,全“1”得“0”)。其逻辑表达式为Y = AB 。

图 2.1.2-3 74LS00 逻辑功能表

2.1.3 BCD 七段数码管显示译码器 部为高电平时,输出端才是低电平(即有“0”得“1”,全“1”得“0”)。其逻辑表达式为Y = AB 。

图 2.1.2-3 74LS00 逻辑功能表

2.1.3 BCD 七段数码管显示译码器

图 2.3-1(a)是共阴式 LED 数码管的原理图,图 2.3-1(b)是其表示符号。使用时,公共阴极接地,7 个 阳极 a~g 由相应的 BCD 七段译码器来驱动(控制),如图 2.3-1(c)所示。图中,电阻是上拉电阻,也称限流 电阻,当译码器内部带有上拉电阻时,则可省去。数字显示译码器的种类很多,现已有将计数器、锁存器、 译码驱动电路集于一体的集成器件,还有连同数码显示器也集成在一起的电路可供选用。

图 2.1.3-1 数字显示译码器

BCD 七段译码器的输入是 4 位 BCD 码(以 D、C、B、A 表示),输出是数码管各段的驱动信号(以 a~g 表 图 2.3-1(a)是共阴式 LED 数码管的原理图,图 2.3-1(b)是其表示符号。使用时,公共阴极接地,7 个 阳极 a~g 由相应的 BCD 七段译码器来驱动(控制),如图 2.3-1(c)所示。图中,电阻是上拉电阻,也称限流 电阻,当译码器内部带有上拉电阻时,则可省去。数字显示译码器的种类很多,现已有将计数器、锁存器、 译码驱动电路集于一体的集成器件,还有连同数码显示器也集成在一起的电路可供选用。

图 2.1.3-1 数字显示译码器

BCD 七段译码器的输入是 4 位 BCD 码(以 D、C、B、A 表示),输出是数码管各段的驱动信号(以 a~g 表示),也称 4―7 译码器。若用它驱动共阴 LED 数码管,则输出应为高有效,即输出为高(1)时,相应显示 段发光。例如,当输入 8421 码 DCBA=O100 时,应显示,即要求同时点亮 b、c、f、g 段,熄灭 a、d、e 段, 故译码器的输出应 Fa~Fg=0110011,这也是一组代码,常称为段码。同理,根据组成 0~9 这 10 个字形的要 求可以列出 8421BCD 七段译码器的真值表。  图 2.1.3-2 BCD 七段译码器真值表

2.1.4 NE555 定时器

555 定时器:555 定时器是一种多用途的数字―模拟混合集成电路,利用它能极方便的构成施密特触 发器、单稳态触发器和多谐振荡器等脉冲电路。由于使用灵活、方便,所以 555 定时器在波形的产生与 交 换、测量与控制、家用电器、电子玩具等许多领域中都得到了应用。 图 2.1.3-2 BCD 七段译码器真值表

2.1.4 NE555 定时器

555 定时器:555 定时器是一种多用途的数字―模拟混合集成电路,利用它能极方便的构成施密特触 发器、单稳态触发器和多谐振荡器等脉冲电路。由于使用灵活、方便,所以 555 定时器在波形的产生与 交 换、测量与控制、家用电器、电子玩具等许多领域中都得到了应用。

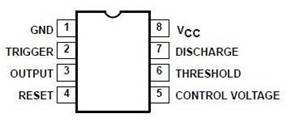

图 2.1.4-1 NE555 定时器功能图

图 2.1.4-1 NE555 定时器功能图

工作原理: 工作原理:

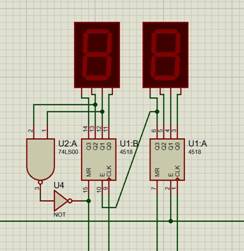

在电源与地之间加上电压,当 5 脚悬空时,则电压比较器 C1 的同相输入端的电压为 2VCC/3,C2 的反 相输入端的电压为 VCC/3。若触发输入端 TR 的电压小于 VCC/3,则比较器 C2 的输出为 0,可使 RS 触发器 置 1,使输出端 OUT=1。如果阈值输入端 TH 的电压大于 2VCC/3,同时 TR 端的电压大于 VCC/3,则 C1 的输 出为 0,C2 的输出为 1,可将 RS 触发器置 0,使输出为低电平。 2.2 时、分、秒计时器的设计 1.“秒”计数器的设计: 将 1 连 1Hz 单脉冲,给 CD4518 提供时钟信号;2 时各位的使能端,连接高电平(+5V);3-6 为输出端,只需分别连到 BCD-SEG 的四边即可;7 是置位端,连到地线或者悬挂,因为秒的个位是十进制,不需要 使用置位;4518 输出端的最后一个(也就是每片计数器的 Q3 端)可以用作级联,用来给下一芯片使能, 所以将 6 连到 10,此时十位计数器是依据个位计数器是否进位来判断是否计时,所以十位的时钟输入不需 要。要达到 60 进制,则十位就是 6 进制,只需要把十进制的”6”这个输出结果引出即可,8421 编码可知 0110 为 6,所以只需要把十位的 Q2 和 Q1 引出即可,将这两个引出端连接到一个与门再反馈到十位的置位 端 MR 即可。  图 2.2-1 “秒”计数器的连线

2.“分”计数器的设计: 图 2.2-1 “秒”计数器的连线

2.“分”计数器的设计:

“分”计数器与“秒”的相同,但要注意“秒”和“分”之间的联接,当“秒”记满 60 过后,“秒” 的十位产生进位信号,只需把这个进位信号引入到“分”计数器的个位的 CLK 端即可。  图 2.2-2 “分”计数器的连线

3.“时”计数器的设计: 图 2.2-2 “分”计数器的连线

3.“时”计数器的设计:

“时”计数器在实现上和前两个计数器无非大同小异,只是需要把进制设计为 24,把十位的“2”和 个位的“4”形成与门送入各位和十位的重置端 MR即可。  图 2.2-3 “时”计数器的连线

2.3 校时电路的设计 图 2.2-3 “时”计数器的连线

2.3 校时电路的设计

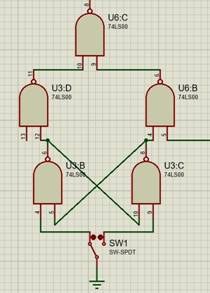

在刚接通电源或者时钟走时出现误差时,则需要进行时间的校准。置开关在手动位置,分别对“时、 分”单独计数,计数脉冲由单次脉冲或连续脉冲输入。有与非门和两个开关组成,实现“时、分”的校准。 当校时开关扳倒右端时,前一个的计时器进位信号送到“分”或“时”计数器的个位 CP 端,进行“时” 计数器和“分”计数器的正常计时。  图 2.3-1 校时电路

当校时开关扳倒左端时,高电平信号送入“时”计数器和“分”计数器的进位脉冲个位 CP 端,每拨动开关一次,“时”和“分”计数器校准时间。

3.总电路图 图 2.3-1 校时电路

当校时开关扳倒左端时,高电平信号送入“时”计数器和“分”计数器的进位脉冲个位 CP 端,每拨动开关一次,“时”和“分”计数器校准时间。

3.总电路图

4.安装调试步骤

4.安装调试步骤

安装过程初始阶段,秒的个位及十位在调试过程中出现了数字显示不全的现象。在连接六进制的过程 中,发现电路只能 4、5 的跳动,后经发现是由于接到与非门的引脚接错一根所至,经纠正后能正常显示。 在连接六进制、十进制、六十进制的进位及十二进制的接法中,要熟悉逻辑电路及其芯片各引脚的功能, 那么在电路出错时便能准确地找出错误所在并及时纠正了。通过安装以及调试过程,最后连接出了可正常 显示“秒"、“分"、“时”的电子钟。 1.设置初始时间为 2 小时 2 分 1 秒。 2. 计时 30 秒后为 2 小时 2 分 31 秒。

2. 计时 30 秒后为 2 小时 2 分 31 秒。

5.故障分析

5.故障分析

“秒”计数器设计时,要注意 Q0-Q3 和 BCD-SEG 的连接引脚,容易颠倒连线导致显数不正确。同时注 意要将十位的 CLK 接地,不能悬挂。 附录(电路元器件清单) 使用器材:74LS00 芯片,CD4158 芯片,BCD 七段数码管显示译码器,定时器,与非门,非门Proteus8.13仿真下载: 数字时钟.zip

(832.71 KB, 下载次数: 22)

2023-5-17 10:49 上传

点击文件名下载附件

下载积分: 黑币 -5

数字时钟.zip

(832.71 KB, 下载次数: 22)

2023-5-17 10:49 上传

点击文件名下载附件

下载积分: 黑币 -5

|

【本文地址】

今日新闻 |

推荐新闻 |

若用时钟下降沿触发,信号由 EN 输入,此时 CP 端为低电平(0),同时复位端 Cr 也保持低电平(0), 只有满足了这些条件时,电路才会处于计数状态,否则没办法工作。

若用时钟下降沿触发,信号由 EN 输入,此时 CP 端为低电平(0),同时复位端 Cr 也保持低电平(0), 只有满足了这些条件时,电路才会处于计数状态,否则没办法工作。