HDLBits第九章练习及答案 |

您所在的位置:网站首页 › 4-1多路复用器电路图 › HDLBits第九章练习及答案 |

HDLBits第九章练习及答案

|

卡诺图到电路

1、三变量2、四变量13、四变量24、四变量35、最小SOP式和POS式6、卡诺图17、卡诺图28、用多路选择器实现卡诺图

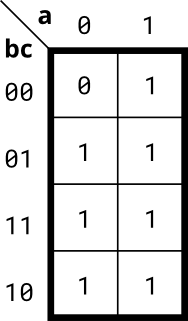

1、三变量

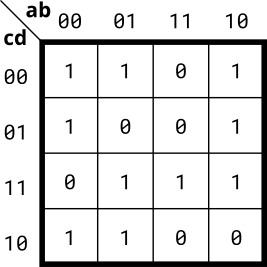

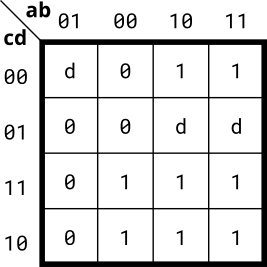

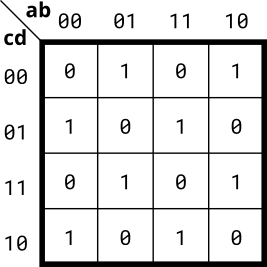

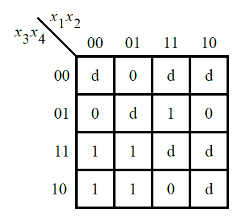

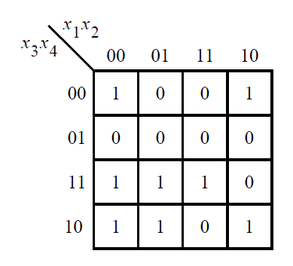

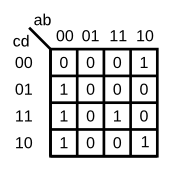

实现下面卡诺图所描述的电路。 验证结果: 实现下面卡诺图所描述的电路。 验证结果: 实现下面卡诺图描述的电路。 代码实现: module top_module( input a, input b, input c, input d, output out ); assign out = a | (a&c) | ((~b)&c); endmodule验证结果: 实现下面卡诺图描述的电路。 验证结果: 真值表: 真值表是表征逻辑事件输入和输出之间全部可能状态的表格。以1表示真,0表示假。 从真值表到标准式 SOP标准式:找出真值表中所有输出为1的表项,按照输入的情况,为1用变量表示,为0则用反变量表示,得出若干乘积项,然后求和。 POS标准式:找出真值表中所有输出为0的表项,按照输入的情况,为1用反变量表示,为0则用原变量表示,得出若干求和项,然后求积。 举例说明 有如下真值表 ABCD00000010010001111001101011011111若针对所有F=1的表项,可轻松写出SOP标准式如下: F=ABC+ABC+ABC+ABC 若针对所有F=0的表项,可轻松写出POS标准式如下: F=(A+B+C)(A+B+C)(A+B+C)(A+B+C) 从标准SOP式到最简SOP式 标准表达式并非最简表达式,从标准SOP式到最简SOP式为一个标准的逻辑化简的过程。 此时可以引入卡诺图,来寻找最小项的合并规律,从而可以轻易的进行化简工作,此处仅介绍系统化简法。 1、求出函数的SOP标准式 例如,对于函数: F=ABC+ABC+D+ABCD 可写出其标准的SOP式为 首先,将最小项按其内部包含1的个数多少进行排列、分组,可得下表: 3、求出必要项、列出化简结果 如果某一个主要项中,至少包含一个其他项不包含的最小项,则它必然是必要项。 得到主要项后再进行验证是否存在等价主要项,并将其删除。 练习: 实现一个有四输入(a.b,c,d)的单输出数字系统,当2、7或15出现在输入端时,生成逻辑1,当0、1、4、5、6、9、10 13或14出现时,生成逻辑0。数字3、8、11和12的输入不会出现在这个系统中。例如,7对应于a和b。c,d分别被设为0,1,1,1。 确定最小SOP格式的输出out_sop和最小POS格式的输出out_pos。 代码实现: module top_module ( input a, input b, input c, input d, output out_sop, output out_pos ); assign out_sop = c & d | ~a & ~b & c; assign out_pos = ~((~c | ~d) & (a | b | ~c)); endmodule验证结果: 实现下面卡诺图所描述的电路。 代码实现: 方法一: module top_module ( input [4:1] x, output f ); assign f = (x[3] & x[4]) | ((~x[1]) & x[3]) | (x[1] & (~x[2]) & x[3]) | (x[2] & (~x[3]) & x[4]) | (x[1] & (~x[3]) & (~x[4])); endmodule方法二: module top_module ( input [4:1] x, output f ); assign f = ~x[1]&x[3] | x[2]&x[4]; endmodule验证结果: 实现下面卡诺图所描述的电路。 代码实现: 方法一: module top_module ( input [4:1] x, output f ); assign f = (~x[1] & x[3]) | (x[2] & x[3] & x[4]) | (~x[2] & ~x[3] & ~x[4]) | (x[1] & ~x[2] & x[3] & ~x[4]); endmodule方法二: module top_module ( input [4:1] x, output f ); assign f = ~x[2]&~x[4] | ~x[1]&x[3] | x[2]&x[3]&x[4]; endmodule验证结果: 对于下面的卡诺图,用一个4-1多路选择器和不限的2-1多路选择器,但2-1多路选择器的使用要尽可能少。你不允许使用任何其他逻辑门,你必须使用a和b作为多路复用器选择器的输入,如下面的4- 1多路选择器所示。 您只实现了标记为top_module的部分,以便整个电路(包括 4 对 1 多路选择器)实现卡诺图。 验证结果: 参考资料: 卡诺图与最简SOP式. |

【本文地址】

代码实现:

代码实现:

代码实现:

代码实现:

注:d可以根据化简需求自己制定为0或是1。

注:d可以根据化简需求自己制定为0或是1。

代码实现:

代码实现:

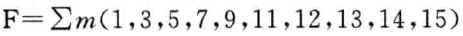

2、求出函数的全部主要项

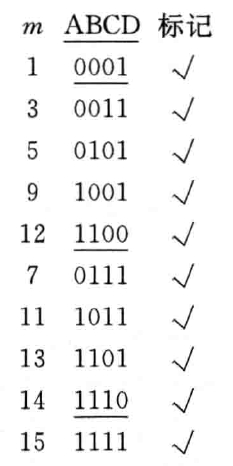

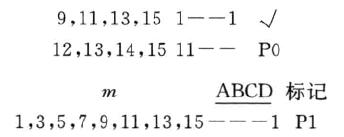

2、求出函数的全部主要项 其次,根据该表,可以发现能合并的两个最小项必定位于相邻的两组,因此从最低组开始,和相邻高位组逐个运算合并,并按乘积项中1的个数进行排列得到的新表如下:(注:1、在合并的同时,需在之前的表中用勾标注出被使用过的最小项;2、如果合并结果与之前某次一样,则无需列出。)

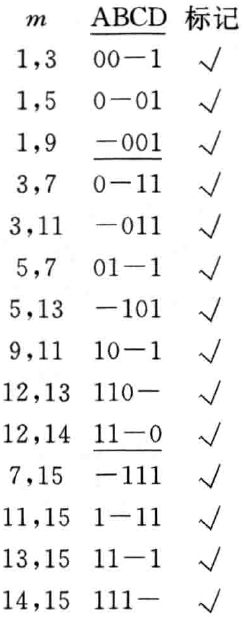

其次,根据该表,可以发现能合并的两个最小项必定位于相邻的两组,因此从最低组开始,和相邻高位组逐个运算合并,并按乘积项中1的个数进行排列得到的新表如下:(注:1、在合并的同时,需在之前的表中用勾标注出被使用过的最小项;2、如果合并结果与之前某次一样,则无需列出。)  第三,参考前两个步骤,继续对表项合并,直至无法合并为止。之后的合并过程需注意的是“—”的位置要相同,继续合并的结果如下:

第三,参考前两个步骤,继续对表项合并,直至无法合并为止。之后的合并过程需注意的是“—”的位置要相同,继续合并的结果如下:

第四,上述各表中,凡是没被“√”标记的合并项,就是主要项。对于该例,主要项就是:P0=AB和P1=D。

第四,上述各表中,凡是没被“√”标记的合并项,就是主要项。对于该例,主要项就是:P0=AB和P1=D。

注:d可以根据化简需求自己制定为0或是1。

注:d可以根据化简需求自己制定为0或是1。

要求:简化 SOP 和 POS 形式的函数。

要求:简化 SOP 和 POS 形式的函数。

代码实现:

代码实现: