【FGPA】VHDL实验 |

您所在的位置:网站首页 › 3-8译码器的vhdl代码 › 【FGPA】VHDL实验 |

【FGPA】VHDL实验

|

实验一 简单的QUARTUSII实例设计 一、 实验目的 1、 通过一个简单的3—8译码器的设计,掌握组合逻辑电路的设计方法。 2、 初步了解QUARTUSII原理图输入设计的全过程。 3、 掌握组合逻辑电路的静态测试方法。 二、 实验原理 3-8译码器三输入,八输出。当输入信号按二进制方式的表示值为N时,输出端标号为N的输出端输出高电平表示有信号产生,而其它则为低电平表示无信号产生。因为三个输入端能产生的组合状态有八种,所以输出端在每种组合中仅有一位为高电平的情况下,能表示所有的输入组合。其真值表如表1-1所示: 输入 输出 A B C D7 D6 D5 D4 D3 D2 D1 D0 0 0 0 0 0 0 0 0 0 0 1 0 0 1 0 0 0 0 0 0 1 0 0 1 0 0 0 0 0 0 1 0 0 0 1 1 0 0 0 0 1 0 0 0 1 0 0 0 0 0 1 0 0 0 0 1 0 1 0 0 1 0 0 0 0 0 1 1

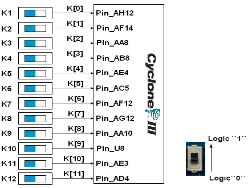

0 1 0 0 0 0 0 0 1 1 1 1 0 0 0 0 0 0 0 表1-1 三-八译码器真值表 译码器不需要像编码器那样用一个输出端指示输出是否有效。但可以在输入中加入一个输出使能端,用来指示是否将当前的输入进行有效的译码,当使能端指示输入信号无效或不用对当前信号进行译码时,输出端全为高电平,表示无任何信号。本例设计中没有考虑使能输入端,自己设计时可以考虑加入使能输入端时,程序如何设计。 三、 实验内容 在本实验中,用三个拨动开关来表示三八译码器的三个输入(A、B、C);用八个LED来表示三八译码器的八个输出(D0-D7)。通过输入不同的值来观察输入的结果与三八译码器的真值表(表1-1)是否一致。实验箱中的拨动开关与FPGA的接口电路如下图1-1所示,当开关闭合(拨动开关的档位在下方)时其输出为低电平,反之输出高电平。

图1-1 拨动开关与FPGA接口电路 LED灯与FPGA的接口电路如图1-2所示,当FPGA与其对应的端口为高电平时LED就会发光,反之LED灯灭。 library IEEE; use IEEE.STD_LOGIC_1164.all; entity Sim381 is port(A,B,C:in STD_LOGIC; Y:out STD_LOGIC_vector(7 downto 0)); end entity Sim381; architecture tmp of Sim381 is signal s:STD_LOGIC_vector(2 downto 0); begin s '0' ) ; elsif Rising_Edge( clk ) then --上升沿 if En = '1' then --En始能端为1 if tmp < 10 then --在0~9时能+1 tmp := tmp + 1 ; else --否则清空 tmp := ( others => '0' ) ; end if ; end if ; end if ; --赋值给CQ CQ Digit Digit Digit Digit Digit Digit Digit Digit Digit Digit Digit Digit Digit Digit Digit Digit null; end case; end if ; end process; end Behaving;

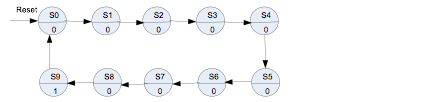

实验五 基于FSM的计数器设计 一、 实验目的 1、 熟悉VHDL的FSM编程。 2、 熟悉FSM的工作原理。 3、 进一步了解实验系统的硬件结构。 二、 实验原理 根据FSM原理,设计十进制计数器状态机,然后根据三进程方法编程。 FSM原理图如图5-1所示。

图5-1 实验原理图

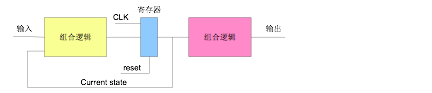

Moore状态机编程结构图如图5-2所示。

图5-2 Moore状态机结构 三、 实验内容 本实验要求完成的任务是在时钟信号的作用下,通过使能端和复位信号来完成加法计数器的计数。实验中时钟信号使用数字时钟源模块的1HZ信号,用一位拨动开关K1表示使能端信号,用复位开关S1表示复位信号,用LED模块的LED1~LED11来表示计数的二进制结果。实验LED亮表示对应的位为‘1’,LED灭表示对应的位为‘0’。通过输入不同的值模拟计数器的工作时序,观察计数的结果。实验箱中的拨动开关、与FPGA的接口电路,LED灯与FPGA的接口电路以及拨动开关、LED与FPGA的管脚连接在实验一中都做了详细说明,这里不在赘述。 library ieee; use ieee.std_logic_1164.all ; entity FSM_Cnt is port( clk , inp , reset : in std_logic; outp : out std_logic_vector( 9 downto 0 ) ); end entity ; architecture behave of FSM_Cnt is type state is( s0 , s1 , s2 , s3 , s4 , s5 ,s6 , s7 , s8 , s9 ) ; signal cur_s , next_s : state ; begin main_process : process ( clk , reset ) begin if reset = '1' then cur_s |

【本文地址】

今日新闻 |

推荐新闻 |