SAR ADC工作原理 |

您所在的位置:网站首页 › 2qs03g工作原理 › SAR ADC工作原理 |

SAR ADC工作原理

|

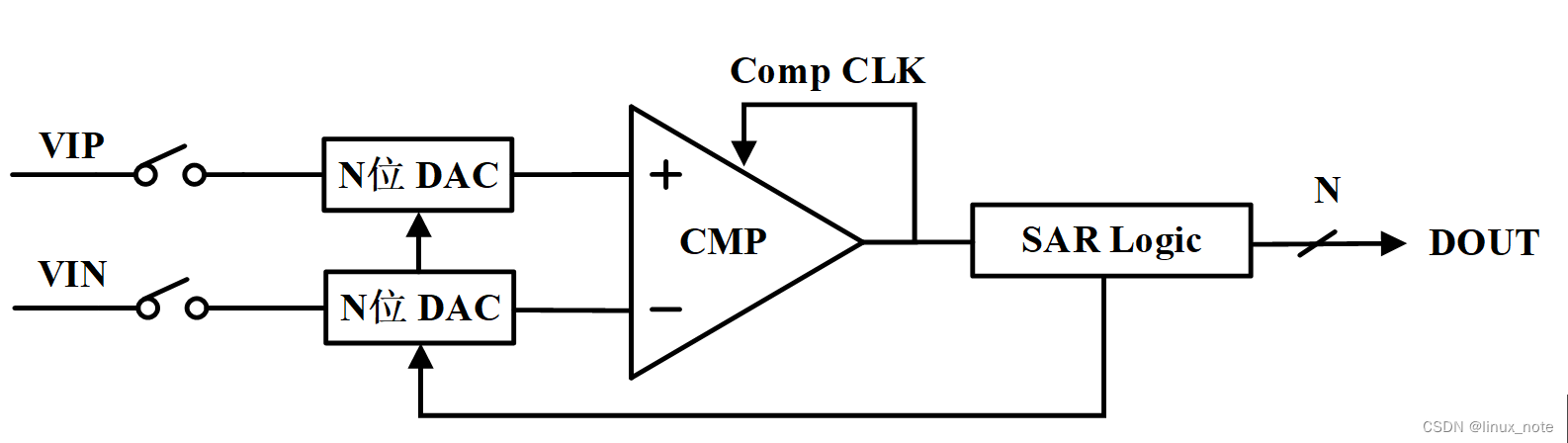

SAR ADC有着电路结构简单的优势,其中的模拟模块只有采样开关和比较器,其余均为数字模块。这不仅使设计变得简单,更是与数字CMOS工艺有着非常好的兼容性。其工作原理也是十分简单,即采用二进制搜索算法对输入信号进行转换。 1.SAR ADC电路结构 图1是一个差分输入的SAR ADC基本结构,其中VIN、VIP为模拟输入。电路主要由采样保持电路、比较器(CMP)、DA转换网络(DAC)、和逐次逼近逻辑(SAR Logic)四个部分构成。其中,采样保持电路由采样开关和采样电容构成(通常采样电容由DAC电容阵列实现),用于将输入模拟信号采样到采样电容上,用于后续的转换;比较器用来比较输入信号与参考信号的大小,输出“0”或“1”一方面用于控制电容阵列的切换,同时存入寄存器等待得到N位数字码后同时输出;DA转换网络是一组二进制权重的电容阵列,由比较器输出控制切换电容上/下极板上的电压,使参考信号以二进制的方式逐次逼近输入信号,此时输出的二进制码即为当前模拟输入对应的数字输出;SAR Logic能够锁存比较器的输出并最终输出N位二进制码。SAR ADC的结构简单,硬件成本低,研究人员也会将其与其他结构相结合以得到更优的性能,例如Pipelined-SAR ADC、单通道采用SAR ADC的时域交织ADC等。

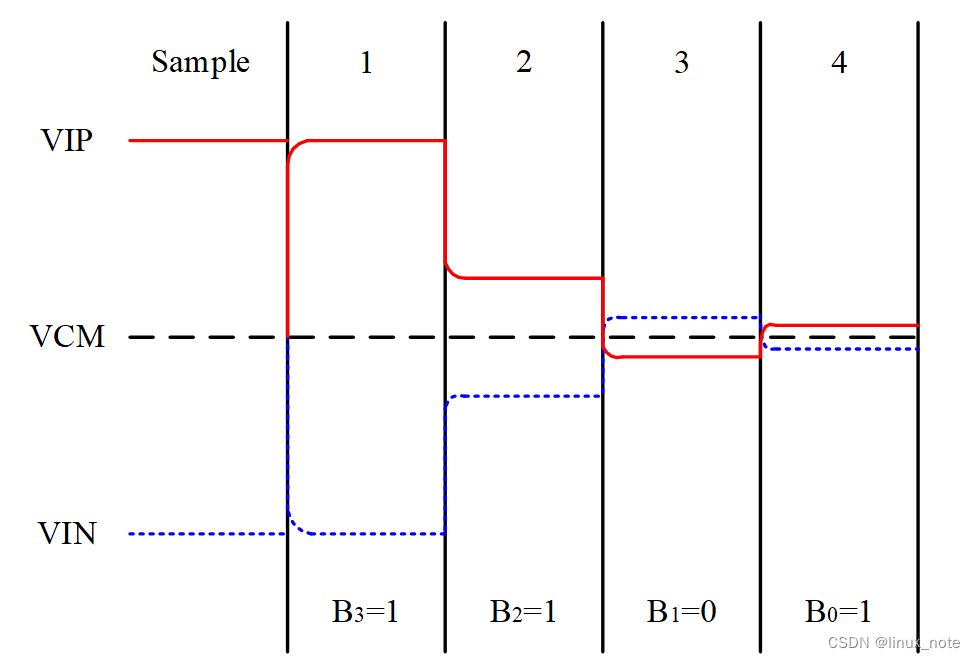

SAR ADC以“二分法”为核心原理,通过对模拟输入信号不断进行二分区间搜索,逐次逼近输入信号所在区间(区间宽度为1LSB),最终得到数字输出来等效模拟输入。对于一个单端输入的SAR ADC,采样到的模拟输入依次与VREF/2、VREF/2±VREF/4、VREF/2±VREF/4±VREF/8……进行比较。当输入信号大于参考电压,比较器输出“1”并且给参考电压加参考电压的一半;当输入信号小于参考电压,比较器输出“0”并且给参考电压减参考电压的一半。根据这种方式不断比较输出,直到结束。

图2 逐次逼近过程示意图 在实际电路中,为了减小噪声对电路的影响,通常采用全差分的电路结构。下面结合图1和图2具体说明SAR ADC的工作原理。首先是采样阶段,采样开关导通时输入VIP和VIN分别给两个充当采样电容的电容阵列充电,当采样开关关断,输入信号保持在采样电容上,为第一次比较做准备。比较阶段,当采样开关关断后时钟控制比较开始。第一次比较VIP和VIN的大小,以图2中以VCM-based开关时序为例,第一次比较时VIP大于VIN输出数字码B3=1,并且通过切换电容阵列上的开关使VIP减小VREF/4,VIN增大VREF/4。此时的输出码B3即为输出数字码的最高位,存储在SAR Logic中等待得到全部数字码后作为最终的输出。VIP和VIN切换后,进行第二次比较,VIP大于VIN输出数字码B2=1(次高位),使VIP减小VREF/8,VIN增大VREF/8。开关切换完成后进行第三次比较,此时VIP小于VIN则输出数字码B1=0,同时给VIP增大VREF/16,VIN减小VREF/16。以四位SAR ADC为例,第四次比较为最后一次比较,比较得到VIP大于VIN则输出B0=1作为最低位,最低位不需要对开关进行切换,得到数字输出码则代表着本次量化结束。 |

【本文地址】

今日新闻 |

推荐新闻 |

图1 SAR ADC基本结构

图1 SAR ADC基本结构